CPU OPERATION AND MEMORY

CPU Components

The CPU comprises several crucial components:

- ALU (Arithmetic Logic Unit): Performs arithmetic and logical operations such as ADD, AND, OR, NOT, etc.

- Control Unit: Decodes instructions and directs operations to other CPU units or external devices.

- Clock: Generates regular pulses to synchronize operations within the CPU and across the system.

- Memory Registers: Fastest storage locations within the CPU used for temporary data storage and manipulation.

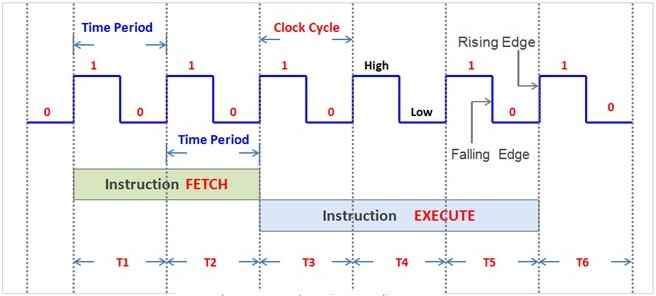

- Measured in Hertz, the clock speed determines the number of instructions a CPU can execute per second.

- One to zero and back to one is one clock cycle.

- The number of clock cycles per second, expressed in GHz (Gigahertz).

- Every time the clock ticks, the CPU processes one instruction.

Operation Execution

Understanding the execution of instructions is important:

- Fetching: Retrieve instructions from the instruction queue.

- Decoding: Interpret the instruction and identify associated operands.

- Operand Retrieval: Obtain necessary data from memory or registers.

- Execution: Perform the specified operation.

- Status Update: Update status flags based on the outcome of the operation.

- Result Storage: Store the result if required.

This sequence, known as the fetch-decode-execute procedure, forms the basis of CPU operation.

Memory Access

Reading from memory involves specific steps:

- Addressing: Specify the memory address to read from.

- Assertion: Signal the CPU’s intent to read from memory.

- Waiting: Allow time for memory to respond.

- Data Retrieval: Copy data from the data bus to the destination.

Memory access (RAM) typically takes longer than register access due to the additional steps involved. Instead of executing only one instruction, I need to execute multiple instructions to access memory.

Caching

To mitigate memory access latency, caching is employed:

- Cache: Stores frequently accessed data closer to the CPU, reducing read and write times.

- Levels: x86 architecture commonly features two cache levels:

- Level 1 Cache: Located within the CPU for rapid access.

- Level 2 Cache: External to the CPU but accessed via a high-speed bus, offering faster access than RAM.

Static RAM is often used in caches due to its efficiency, though it’s costlier than dynamic RAM. Dynamic RAM is used in main memory due to its lower cost and higher storage capacity.